SPIE2008においてNGR2100事例発表、好評を博す

半導体大手、東芝/Samusung/Hynix応用事例発表【概要】

株式会社トプコンは、株式会社ナノジオメトリ研究所(以下NGR)と共同で、電子ビーム技術をベースとした高精度・高スループットの設計データを用いた半導体電子ビームパターン検査装置の開発を行いました。そしてNGRよりパターンジオメトリ検証システムNGR2100を国内外の有力デバイスメーカーに納入いたしました。

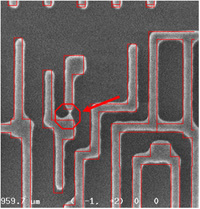

半導体プロセスの微細化に伴って、パターンサイズがリソグラフィー(露光)波長より大幅に小さくなり、歩留まり低下要因の一つとしてシステマティック欠陥*¹が増加する傾向にあり、電子ビームを用いた計測技術の必要性が増しております。NGR2100は電子ビームによるDie to Database検査が可能であり、プロセスの微細化には必至のツールとして注目されています。

2008年2月24日〜29日に米国カリフォルニア州サンノゼ市で開催された、半導体業界で最も権威のある最先端半導体技術コンファレンス「SPIE Advanced Lithography 2008*²」において世界最先端半導体メーカーである東芝セミコンダクター社、Samsung Electronics、Hynix Semiconductorの3社およびNGRから、NGR2100の応用成功事例に関する論文が発表され、大きな反響をよびました。パターンジオメトリ検証システムNGR2100が半導体製造プロセスでどのように有効であるかが各社の発表で確認されましたので、当社はNGRと共に当システムを中心とした電子ビーム応用製品の事業拡大に努めて参ります。

【NGR2100の特徴】

NGRは、2004年にパターン形状及び設計に起因する欠陥の検査・検証に対応するパターンジオメトリ検証システム「NGR2100」を世界で初めて開発しました。NGR2100は、設計技術であるCAD技術とパターン検証技術を統合したCAD/SEMマッチング及び形状計測機能により、実ウェハ上で得られた電子ビーム画像から2次元の輪郭出力を抽出して、設計データと直接比較して検証します。NGR2100はOPCに関わる設計・プロセス起因の歩留まり低下に影響するパターンを検証(Die-to-Database Verification)できる、他に類のない装置です。45nm及び32nm世代に対応が可能であり、革新的な開発サイクルタイムの短縮・歩留まり向上に貢献しております。

アプリケーション

- システマティック*¹欠陥検出

- DFM*³(設計/OPC/マスク)へのフィードバック

- OPC*4検証

- クリティカルジオメトリ検証*5

- FEM*6 、ACLV*7等の解析

- PWQ*8 計測

【SPIEで好評】

次世代露光技術に注目が集まる‐先端計測技術の進展に期待

今回のSPIEでは、DBM*9 (Design Based Metrology)が32nm以降の次世代デバイス製造における計測技術として認知されつつあります。実ウェハ上で設計データと2次元電子ビーム画像の輪郭外形出力パターンを直接比較が可能なNGRの技術に一層の注目が集まりました。Design – OPC*4 – Simulation – Mask – Scanner – Waferの一連の半導体製造工程が、今までにも増して密接に関連せざるをえない状況であり、NGR2100を使った総合的なフィードバック系DFM*³( Design For Manufacturability)の構築が先端半導体各社の課題となっています。特に、32nmノードの製造では、リソグラフィ技術のみではなくエッチング技術、膜付技術も含めた総合技術となり、これらに対する計測手段が現時点では確立されておりません。しかしNGRの計測技術がその唯一の解であるとの評価が確立されつつあります。

今回のカンファレンスにおいて各国の半導体デバイスメーカーや半導体製造装置メーカーの関係者が多数聴衆しており、NGR2100への注目と期待の大きさが確認できました。

【各社の発表概要】

東芝セミコンダクター社

シミュレーション・マスクパターン・転写パターンの相関を検証

橋本氏他の論文(Hot Spot Management with Die-to-Database Wafer Inspection System)では、NGR2100を適用することにより致命的なHot Spotの検出が可能となり、開発段階でのTAT*10 (Turn-Around-Time)の大幅短縮が可能となったことを紹介しています。

Samsung Electronics

OPC処理の最適化解析によって、OPC処理精度の向上

Jeong-Geun Park氏他論文(Systematic Defect Inspection and Verification for Distributions of Critical Dimension in OPC Models Utilizing Design Based Metrology Tool)では、微細化の進行により、CDコントロール、Systematic Defect 検査、OPCベリフィケーションが歩留まり改善に不可欠で、DBM*9 (Design Based Metrology)ツールであるNGR2100を適用することによりChip全面CD計測を行い、OPCプロセス改善を図ることが可能となったことを報告しています。

HYNIX Semiconductor

リソグラフィー工程全体の最適化に貢献

Hyunjo Yang氏他の論文(Wide Applications of Design Based Metrology with Tool Integration)では、DBM(Design Based Metrologies)においてマスクデータ、シミュレーション、ウェハ転写結果の相関を検証することの重要性を述べて、その中でNGR2100が果たす重要な役割の実例を説明しています。

NGR

北村正 他の論文(A New Robust Process Window Qualification (PWQ) Technique to Perform Systematic Defect Characterization to Enlarge the Lithographic Process Window using a Die-to-Database Verification Tool (NGR2100))では、Die-to-Database VerificationツールであるNGR2100を使って、リソ工程のプロセス・ウインドーを大きくするために、有効な新しいProcess Window Qualification (PWQ)手法を説明しています。

【今後の取り組み】

当社の半導体向け検査装置(電子ビーム応用装置) は、電子ビーム技術と精密加工技術を基に開発されています。今後の半導体微細化の進展に伴い、半導体の開発・製造プロセスでは益々必要性が高まるとともに、マーケットの拡大が予想されます。当社ファインテックビジネスにおいては、電子ビーム応用装置は今後主力となる重要な領域であり、引き続きこの分野に注力して参る予定です。

また、当社はNGRとのアライアンスをさらに強化し、半導体向け検査装置の改良/開発を推進し、パターンジオメトリ検証システムを主力製品として電子ビーム応用製品の事業拡大に邁進いたします。

用語の解説

*1 システマティック欠陥:半導体製造に対する、デザイン・プロセス余裕度不足によるパターン形状及び設計起因の欠陥

*2 SPIE2008:2008年2月24日〜29日米国カリフォルニア州サンノゼで開催された半導体業界で最も権威のある最先端半導体技術コンファレンス

*3 DFM:(Design For Manufacturability):設計における変動の影響を評価して歩留まり向上につなげる製造性考慮設計技術

*4 OPC(Optical Proximity Correction):リソグラフィー(露光装置)転写により生じるパターンの変形を予想して、予めマスクパターンに補正を加えて所定のパターン寸法を得るためのマスクパターン補正技術

*5 クリティカルジオメトリ検証:リソグラフィーのマージンが得られていないパターンデータの致命的欠陥箇所-Killer欠陥=Hot Spot-を抽出

*6 FEM (Focus Exposure Matrix):リソグラフィー工程でのプロセス誤差・変動幅を抑えるために露光装置の露光量とフォーカス変動の影響を調べる手法

*7 ACLV(Across the Chip Line Width Variation):露光装置の収差の影響によるウェハのショット内の中心と周辺のばらつき

*8 PWQ(Process Window Qualification):露光装置の露光量とフォーカスバジェットの最適範囲

*9 DBM (Design Based Metrology) : 設計に基づき設計データ処理から直接パターンプロセスを改善するための計測技術

*10 TAT(Turn around time):ニューモデル開発、プロセス開発サイクルタイム短縮で歩留りの早期立上げ